TÜTEL

EUPILOT

The European Pilot (EUPILOT) Project

The European Pilot (EUPILOT) Project is a project carried out by an international consortium led by Barcelona Computing Center and including TÜBİTAK. This project was initiated under the Horizon 2020 EuroHPC-RIA call and aims to develop an accelerator. Accelerators provide the majority of the performance in modern High Performance Computing (HPC) systems and are the fundamental building blocks of Exascale systems. This project aims to provide the first example of European designed, implemented and built HPC and High Performance Data Analytics (HPDA) (AI, ML, DL) accelerators.

The European Pilot combines an all-European full stack software, open source software (SW) and open source hardware (HW) based on RISC-V accelerators that connect to any general purpose processor (CPU) via PCIe Gen 6.0 or CXL 3.0. The accelerators will be built on Global Foundries' advanced 12 nm silicon technology. The project combines SW/HW co-design to run key applications and libraries in a complete software stack, including middleware, compilers, and tools for the RISC-V ecosystem.

The European Pilot Project aims to produce a prototype that leverages and improves upon other European projects such as EPI, MEEP, POP2 CoE, EuroEXA and ExaNeSt. The project will be implemented by combining existing IP, FPGA based hardware emulation and real ASIC prototypes, demonstrating the feasibility of hardware and software. Within the scope of the project, various applications from AI to HPC will be used, and the aggressive ASIC implementation will be the smallest technology node produced in Europe and can be easily adapted to HPC applications in the near future.

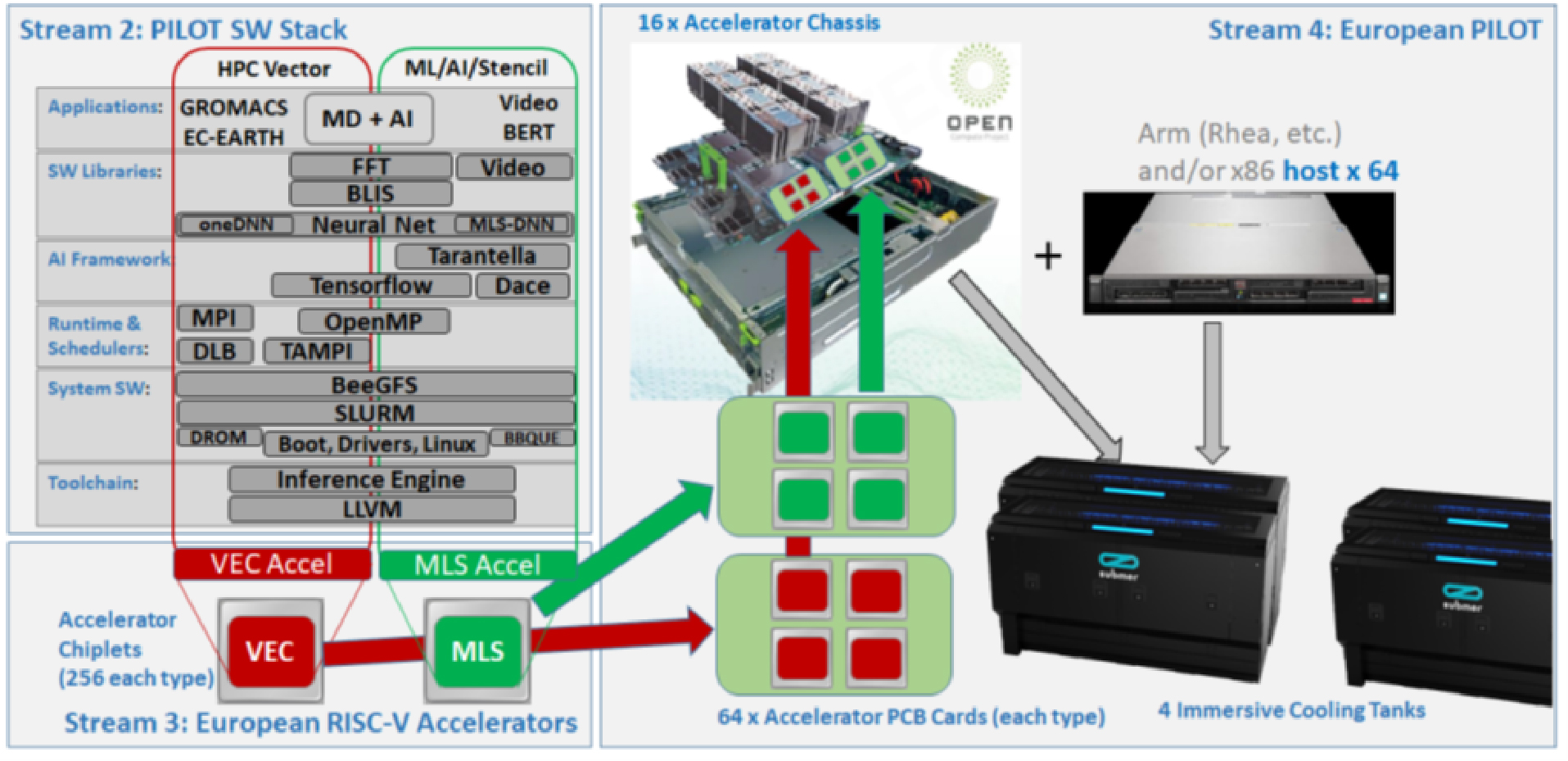

The main components of The European Pilot Project are shown in Figure 1. As TÜBİTAK, our tasks in the project have been determined as follows:

- Solution of molecular dynamics equations on accelerator system and emulator for the development of HPC and AI (Artificial Intelligence) applications.

- Design and integration of the Bandgap IP, temperature and voltage sensor required for the accelerator system and the digital block design that controls this sensor using Global Foundries (GF) 12nm technology.

- Design of the test chip controller to test the PHY and IP modules to be used in MLS and VEC chips.

- Supporting the background design and integration of vector and MLS chips into the system using GF12nm technology.